Initial parts are general-purpose and consigned to what Renesas has named the RA8M1 group of the RA8 series.

Common specs of RA8M1 parts are: 480MHz Cortex-M85 with Helium and TrustZone, 1 or 2Mbyte programme flash, 12kbyte data flash, 1Mbyte sram, octal SPI with execute-in-place and decryption-on-the-fly, CAN-FD, Ethernet, USB (full/high speed), 16bit camera interface and I3C serial. Package options are 224pad BGA, or LQFP with 100, 144 or 176 pads.

Eight parts in total have been introduced, giving all four package options, with 1 or 2Mbyte of programme flash.

“Renesas today introduced the world’s most powerful microcontrollers,” it claimed, “delivering performance over 3000 CoreMark points, and deterministic low-latency real-time operation. RA8 Series MCUs are the industry’s first to implement the Arm Cortex-M85 processor, enabling the devices to deliver 6.39 CoreMark/MHz. This performance will allow designers to use the MCUs in applications that previously required microprocessors.”

Arm’s Helium vector extension are included for DSP and machine learning algorithms, said by Renesas to make such processing four times faster compared with using a Cortex-M7 processor.

“RA8 series MCUs enable edge and end-point devices to implement natural language processing in voice AI and predictive maintenance applications, using Helium to accelerate the neural network processing,” it added.

Security is high on the last of priorities with these MCUs: the company has designed RA8 series for PSA Certified Level 2 + secure element, NIST CAVP, and FIPS 140-3 certification.

To support this, Arm’s TrustZone provides a protected hardware environment for hypervisor code, and Renesas’ ‘RSIP-E51A’ hardware accelerates cryptography (AES, RSA, ECC, HASH, 128bit ID) and supports secure boot.

“Other security features include immutable storage for a hardware root-of-trust, octal SPI with decryption-on-the-fly, secure authenticated debug, secure factory programming and tamper protection,” said Renesas. The Armv8.1-M architecture employed in the core introduces pointer authentication and branch target identification (‘PACBTI’, see below) security extension to mitigate “software attacks targeting memory safety violations and memory corruptions”.

To reduce power consumption, independent power domains have been implemented as well as low power modes and fast wake-up.

For development, the ‘RA8M1 group evaluation kit’ (RTK7EKA8M1S00001BE, right) is shipping.

Stay up to date with the latest in industry offers by subscribing us. Our newsletter is your key to receiving expert tips.

The artificial intelligence(AI) boom is triggering an unprecedented expansion race among the world's largest memory chipmakers.Surging demand for high-bandwidth memory (HBM) and high-performance D

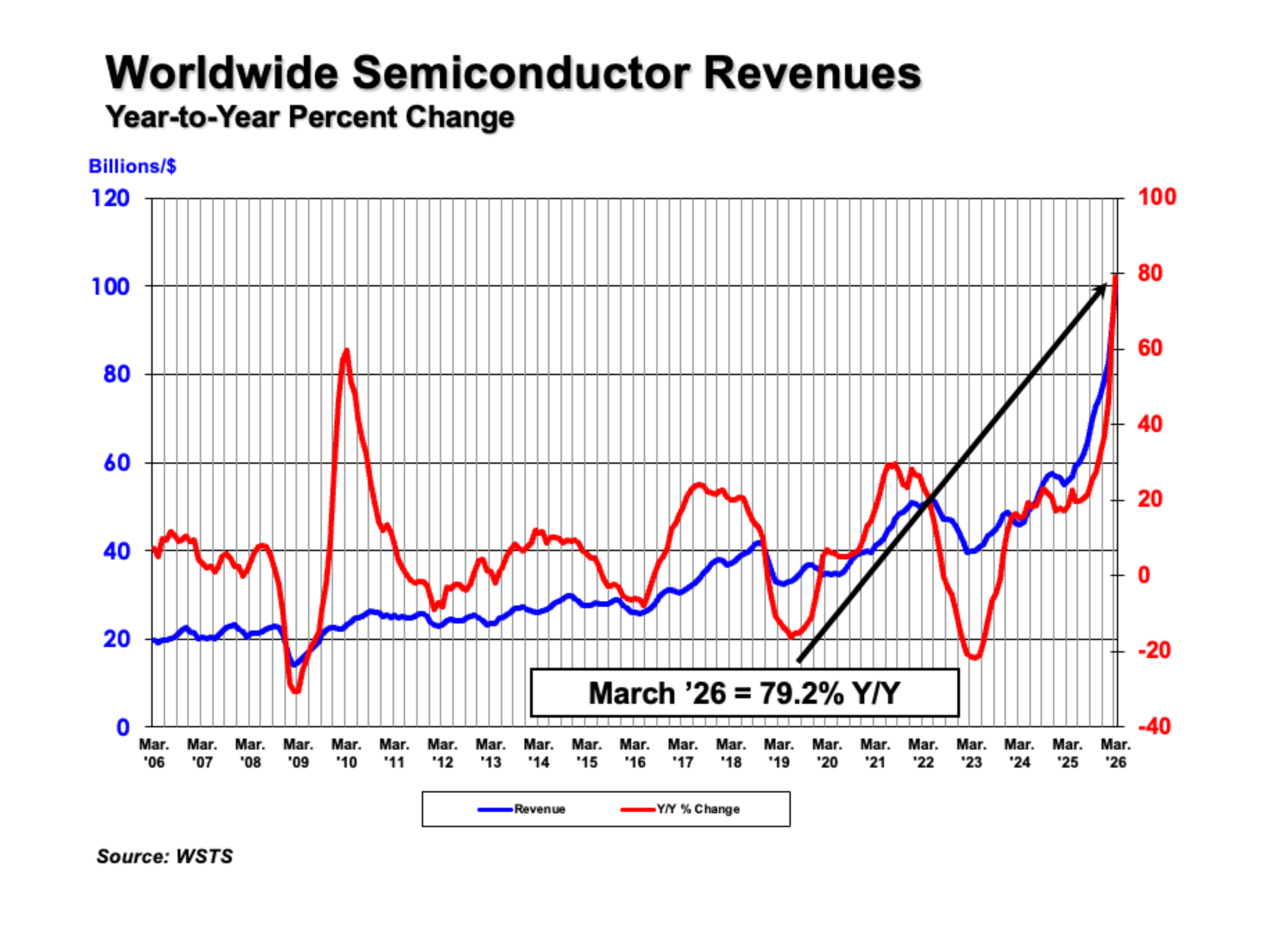

The Semiconductor Industry Association (SIA) today announced global semiconductor sales were $298.5 billion during the first quarter of 2026, an increase of 25% compared to Q4 of 2025. Global sales we

Texas Instruments (TI) reported robust results for the first quarter of 2026 on April 23, driven by surging AI data center demand and a notable rebound in industrial control applications. TI stressed